# An effective method of lowering partial products involves merging additions and accumulations into a multiply-accumulate unit.

# <sup>1</sup>B. Bhargavendera, <sup>2</sup>B. Thirupathi, <sup>3</sup>T. Nageswhar Rao, <sup>4</sup>B Vasanth Goud

<sup>1,2,3</sup>Associate Professor, <sup>4</sup>UG Student, <sup>1,2,3,4</sup>Department of Electronics and Communication Engineering, Vaageswari College of Engineering, Karimnagar, Telangana, India

#### **ABSTRACT**

This research suggests a pipelined Mac architecture with minimal power and fast performance. Carry propagation of ads has higher power consumption and longer route latency; to address this issue, we suggest a way. In this, we include a portion of additions into a procedure that only partially reduces the result. The PPR procedure of subsequent multiplication does not accomplish addition or accumulation of MSB bits. The total number of carries is meant to be accumulated by a small size adder in order to properly contrast with surplus in the PPR process. Using XilinxISE14.7, the efficacy of the suggested technique is calculated.

Keywords: MAC unit, dadda multiplier, Arithmetic circuits, alpha-bit adder

#### Introduction

In the proposed method we use two stage MAC unit with 8 and 16 bit. In Partial Product Generation (PPG) process, PPR performed in the first stage, in the second stage performs the  $(k+\alpha)$ -bit addition to produce the accumulation result. The main trademark of this proposed architecture is mentioned below: To reduce the lengths of carry propagations, we integrate a part of additions into the PPR process. To handle overflow in the PPR process, a  $\alpha$ -bit adder is used to count the total number of carries. By applying the gating technique, the second stage can only be executed in the last cycle (of the entire sequence of multiply-accumulate operations) for power saving.

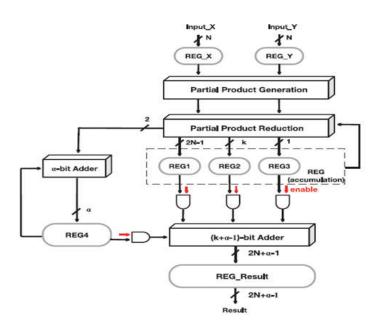

Fig.1. Architecture of Proposed MAC Unit

The proposed architecture of MAC shown in above figure. Our PPM (for the PPR process) is composed of two

ISSN: 0950-0707

PPMs: one PPM is derived by the PPG and the other PPM is derived by the accumulation. In the first stage of proposed MAC, the final addition of higher significance bits is not performed. Register *accumulation* is used to store the PPM derived by the accumulation. Thus, register *accumulation* includes three parts: REG1 (i.e., the first row) has 2N-1 bits, REG2 (i.e., the second row) has k bits, which can define by the user, and REG3 (i.e., the third row) has I bit. In the PPR process, we adopt the Dadda tree approach to reduce our PPM to two rows. After our PPM is reduced to be two rows, we perform the (2N-k-1)-bit final addition. Since we use an (2N-k-1)-bit adder for the addition of the last two rows obtained by the Dadda tree approach, a larger k can have a smaller carry propagation in the (2N-k-1)-bit adder. However, since the final addition and accumulation of k higher significance bits are performed in the PPR process of the next multiplication, a larger k results in a larger PPM for the PPR process. In the second stage of the proposed MAC unit, we produce the accumulation result. The inputs of the second stage include register *accumulation* (consisting of REG1, REG2 and REG3) and register REG4. In the proposed MAC unit, the accumulation has been done in both the  $\alpha$ -bit addition and the next PPR process. Thus, if we only need to obtain the final result in the last cycle, we can disable the  $(k+\alpha)$ -bit addition in other cycles for power saving.

#### **Advantages**

Low power consumption

Carry propagation is not considered in this method and hence delay will be reduced

#### **Applications**

DSP

Image processing Audio Applications

### **Related Work**

Two carry propagations—adds in multiplication and additions in accumulation—must be carried out in the traditional MAC unit. The dada multiplier is used for multiplication in the MAC unit. The Dadda method varies from the Wallace method in that it only uses the bare minimum of full and half adders to achieve predefined stage heights. The stage height restrictions are as follows: #2, #3, #4, #6, #9, #13 #19 #28 #42 The size of each stage is 1.5 times that of the stage above it. The usage of complete adders, which take three partial products and turn them into two partial products, produces the 1.5 reduction ratio. Thus the maximum height of the succeeding stage is ½ that of the previous stage. In doing this, Dadda seeks to optimize the area of the multiplier by using the fewest number of adders to reach the CPA stage.

ISSN: 0950-0707

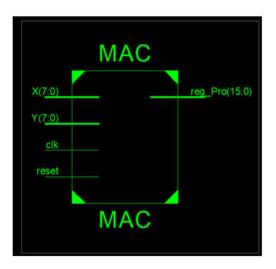

# SIMULATION RESULTS RTL

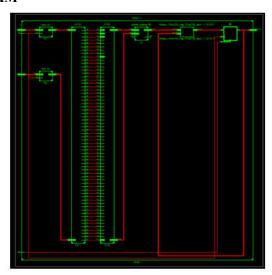

# INTERNAL BLOCK DIAGRAM

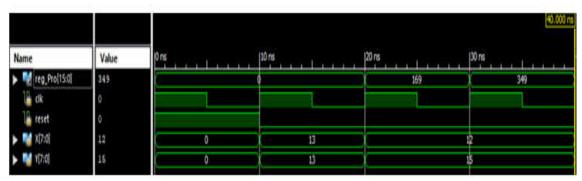

# SIMULATION RESULTS

#### **CONCLUSION**

We have seen different application of MAC unit for the various application. MAC unit designed with various multiplier among them Booth's multiplier is having highest operating speed and consumes less power. MAC unit is high in demand in Digital signal processing to provide the basic hardware for the systems. MAC unit is in use for all type of arithmetic operation such as addition multiplication, division, squares and square-root. MAC unit must be superior in terms of area, delay, power consumption, speed and complexit

#### REFERENCES

- 1. Meenu S Ravi1, R H Khade and Ajit Saraf, "Design of Fast Floating Point Multiply Accumulate Unit using Ancient Mathematics for DSP Applications." European Journal of Advances in Engineering and Technology, pp.55-59, 2015.

- 2. Ku. Shweta N. Yengade, Associate Prof. P. R. Indurkar, "Review On Design Of Low Power Multiply And Accumulate Unit Using BaughWooley Based Multiplier." International Research Journal of Engineering and Technology (IRJET) Volume: 04 Issue: 02 Feb -2017.

- 3. Shaik Nasar, K. Subbarao, "Design & Implementation of MAC Unit Using Reversible Logic." International Journal of Engineering Research and Applications (IJERA) Vol. 2, Issue5, September-October 2012, pp.1848-1855

- G.Indira, G. Madhusudhana Rao, P.Jaya Babu, M. Ravi Kiran, "An Efficient Architecture of MAC Unit with LAW Multiplier." International Journal of Advanced Scientific Technologies in Engineering and Management Sciences (IJASTEMS-ISSN: 2454-356X) Volume.2, Issue.11, November.2016

- 5. Saleh, Hani, and Earl E. Swartzlander, "A floating-point fused add-subtract unit." In 2008 51st Midwest Symposium on Circuits and Systems, pp. 519-522. IEEE, 2008.

- 6. Samy, Rodina, Hossam AH Fahmy, RamyRaafat, Amira Mohamed, Tarek ElDeeb, and Yasmin Farouk, "A decimal floating-point fused-multiply-add unit." In 2010 53rd IEEE International Midwest Symposium on Circuits and Systems, pp. 529- 532. IEEE, 2010.

- 7. Michael F. Cowlisha, "Decimal FloatingPoint: Algorism for Computers." Proceedings of the 16th IEEE Symposium on Computer Arithmetic (ARITH'03) IEEE, 2003

- 8. A. D. Robison, "N-Bit Unsigned Division via N-Bit Multiply-Add," Proceedings of the 17th IEEE Symposium on Computer Arithmetic, pp. 131-139, 2005.

- 9. Singh, Harpreet, and Chakshu Goel, "Design Approaches for a Novel Reversible 4-bit Comparator." IJMSC-International Journal of Mathematical Sciences and Computing (IJMSC) (2015).

ISSN: 0950-0707